Inscription / Connexion Nouveau Sujet

Inverseur CMOS

Bonsoir,

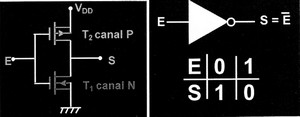

Ci-joint est illustré le schéma et la table de vérité d'un inverseur CMOS (association d'un transistor P-MOS et d'un N-MOS).

Pourriez-vous m'expliquer à partir de ces schémas comment un état haut en entrée se transforme en état bas en sortie et inversement (électrons, trous, etc..)?

Merci d'avance.

Les 2 transistors (canal P et canal N) sont à enrichissement (enhancement en anglais), c'est à dire qu'ils sonts bloqués pour une faible tension Gate-Source.

... Et allumés si la tension gate-source est suffisante (et dans le bon sens).

La source du transistor canal P est à +Vcc et la source du transistor canal N est au 0 Volt.

Les gates les 2 transistors sont connectées ensemble à l'entrée E.

Si l'entrée E est à 1 logique (près de +Vcc), le transistor canal P a une tension gate-source quasi nulle et il est bloqué.

Alors que le transistor canal N a une tension gate-source de quasi +Vcc, il est donc conducteur (entre son drain et sa source).

La sortie S est alors tirée vers le 0 Volt par le transistor canal N.

Si l'entrée E est à 0 logique (près de 0 V), le transistor canal P à une tension gate-source de quasi -Vcc et il est conducteur (entre son drain et sa source).

Alors que le transistor canal N a une tension gate-source quasi nulle, il est donc bloqué.

La sortie S est alors tirée vers le +Vcc par le transistor canal P

Quelques mots sur les transistors MOS sur ce lien : ![]()

Dans le cas de l'inverseur CMOS, il s'agit comme je l'ai précisé de transistors à enrichissement (enhancement).