Inscription / Connexion Nouveau Sujet

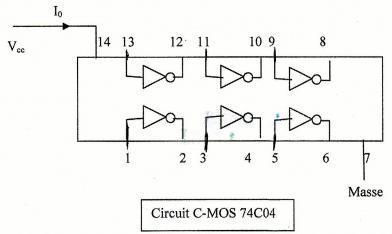

circuit C-MOS 74C04

Bonjour voici l'exercice dont je dois resoudre:

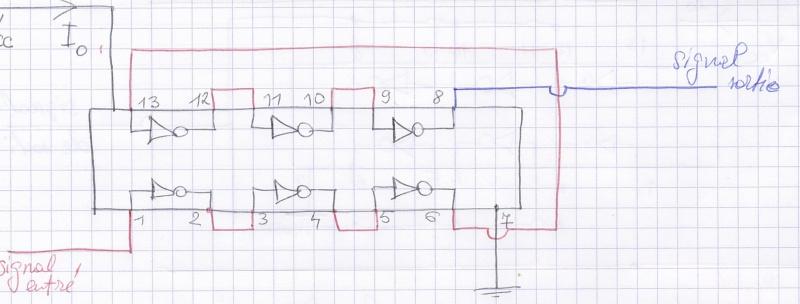

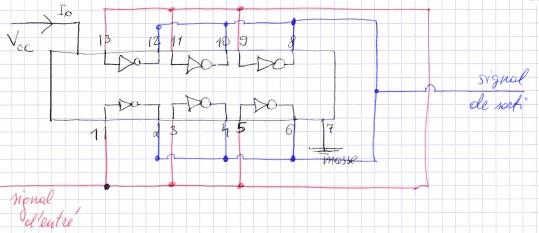

voici le branchement

d'apres se que j'ai compris il s'agit des transisteurs qui fonctionent en operation logique NON-ET (nand en anglais)

mais pour formuler la puissance consommé P0, faut-il passer par l'amplitude du fondamental pour un signal carré?, ou V=(2*E0)/ , puis faire P0=V0*I0?

, puis faire P0=V0*I0?

peut-être je n'ai pas bien compris la question, mais pourriez-vous me guider?

Merci

***Enoncé scanné supprimé et images recadrées***

Bonjour ,

ton branchement des portes ne me semble pas correct . Je pense qu'il faut les mettre en série et pas en parallèle .

Ensuite , c'est la puissance absorbée par le composant qui est mesurée (Po = 5 Io)

C'est pas celle du générateur BF

Et on découvre que plus la fréquence du générateur augmente , plus le composant consomme de la puissance continue . Sa température va mêmes'élever .

Cordialement

Étant donné le fait que toutes les composantes du dispositif possèdent les mêmes caractéristiques, l'ordre de branchement n'a pas d'importance, c'est pour cela que j'ai relié le 6 à la 13.

Relié de la manière présenté dans l'image, le dispositif ne fonctionnera pas lui comme un simple fil conducteur?

Et si on lui appliquera une valeur logique 1 (une tension sur la borne 1) cessera-t-il la conduction, le passage de I0?

Par la même occasion je vais reéditer l'énoncé de l'exercice:

1. on veut mesurer le courant d'alimentation I0 du composant lorsqu'on lui impose un signal logique en créneau formé d'une suite de 0 et 1. Le signal est appliqué par un générateur basses fréquences de fréquence f à la borne 1 du composant. Comment doit-on brancher les autres entrées pour que la consommation du composant soit maximale? Formuler la puissance consommée P0.

2. Pour une fréquence f=100 kHz on mesure I0=0.065 mA et pour f=1000 kHz on mesure I0=0.65 mA. Calculer la puissance consommée dans chaque cas. Conclure sur l'influence de la fréquence. (VCC=5V)

Merci d'avance pour votre aide.

Le branchement est maintenant correct .

Il reste 2 opérations à faire (P=U . I puisqu'on est en courant continu) et constater que quand la fréquence d'agitation des portes est multipliée par 10 , la puissance absorbée par le circuit est aussi multipliée par 10 .

Et pour cette qestion? :

Relié de la manière présenté dans l'image, le dispositif ne fonctionnera pas lui comme un simple fil conducteur?

Et si on lui appliquera une valeur logique 1 (une tension sur la borne 1) cessera-t-il la conduction, le passage de I0?

Si le circuit ne fait plus de commutations , il consommera quand même un courant Io certes très faible mais non nul .

Ce qui serait intéressant, même si ce n'est pas demandé, c'est d'essayer de comprendre les raisons pour lesquelles Io augmente avec la fréquence.

Le monde appartient aux curieux de tout.

Une explication un peu simpliste : à chaque basculement le composant utilise de l'énergie pour propager ce basculement de l'entrée vers la sortie . Plus il y a de basculements , plus l'énergie consommée sera grande .

Oui, c'est un peu simpliste.

La cause majeure (pas la seule, mais largement prépondérante) est la présence de capacités parasites entre les différentes parties des transistors :

Sur mon dessin :

A gauche une représentation d'un gate Cmos (inverseur) telle qu'on la voit souvent.

A droite, j'ai ajouté les capacités "parasites" présentes (capacité drain-gate, drain-source, source-gate pour les 2 transistors complémentaires)

Les courant de charges et décharges de ces différents capacités sont fournies par l'alimentation et bien entendu, la puissance tirée sur l'alimentation est alors proportionnelle aux nombres de charges et décharges pour un temps donné ... donc à la fréquence des basculements.

Dans les data sheet de la porte, on trouve souvent la capacité vue de l'entrée du Cmos (6 pF pour ce type de gate) mais on donne rarement tout ce qu'il faut pour trouver les autres.

Sauf distraction